**Technology & Sciences**

June-2016 Volume 3, Issue-6

Email:editor@ijarets.org

www.ijarets.org

# SCHEME OF REDUCED CONTROL LINES IN MULTIPLEXER PERFORMING THE REVERSIBLE ALU

**P. Karthika** Student Department of Applied Electronics Infant Jesus College of Engineering Tamil Nadu A. Rathinavel Pandian

Assistant Professor Department of ECE St. Mother Theresa Engineering College Tamil Nadu

**ABSTRACT:** Reversible or information-lossless circuits have applications in digital signal processing, communication, computer graphics and cryptography. Reversibility plays an important role when energy efficient computations are considered. Reversible logic is used to reduce the power dissipation that occurs in classical circuits by preventing the loss of information. This paper proposes a reversible design of a 16 bit ALU. This ALU consists of eight operations, two arithmetic and five logical operations. The arithmetic operations include addition, subtraction, and the logical operations include NAND, AND, OR, NOT and XOR. All the modules are being designed using the basic reversible gates. The power and delay analysis of the various sub modules is performed and a comparison with the traditional circuits is also carried out.

**KEYWORDS** - Reversible logic circuits, Reversible logic gates, Reversible adder/Subtractor, Reversible logic unit, Reversible ALU.

# **1. INTRODUCTION**

In modern VLSI system power dissipation is very high due to rapid switching of internal signals. The complexity of VLSI circuits increases with each year due to packing more and more logic elements into smaller volumes. Hence power dissipation has become the main area of concern in VLSI design. Reversible logic has its basics from thermodynamics of information processing. According to this, traditional irreversible circuits generate heat due to the loss of information during computation. In order to avoid this information loss the conventional circuits are modeled using reversible logic. Landauer [1961] showed that the circuits designed using irreversible elements dissipate heat due to the loss of information bits [1]. It is proved that the loss of one bit of information results in dissipation of KT\*log2 joules of heat energy where K is the Boltzmann constant and T is the temperature at which the operation is performed. Benett [1973] showed that this heat dissipation due to information loss can be avoided if the circuit is designed using reversible logic gates [2]. A gate is considered to be reversible only if for each and every input there is a unique output assignment. Hence there is a one to one mapping between the input and output vectors. A reversible logic gate is an n-input, n- output device indicating that it has same number of inputs and outputs. A circuit that is built from reversible gates is known as reversible logic circuit. In this paper, we design a 16 bit reversible ALU that can perform eight operations simultaneously. The eight operations include addition, subtraction, multiplication, division, AND, OR, NOT and XOR. All the modules are simulated in modelsim SE 6.5 and synthesised using Xilinx ISE 12.2.

# 2. REVERSIBLE GATES

Reversible logic is gaining importance in areas of CMOS design because of its low power dissipation. The traditional gates like AND, OR, XOR are all irreversible gates. Consider the case of traditional AND gate. It consists of two inputs and one output. As a result, one bit is lost each time a computation is carried out. According to the truth table shown in Fig.1, there are three inputs (1, 0), (0, 1) and (0, 0) that corresponds to an output zero. Hence it is not possible to determine a unique input that resulted in the

### International Journal Of Advanced Research In Engineering Technology & Sciences ISSN: 2394-2819 Email: editor@ijarets.org June- 2016 Volume 3 Issue-6 www.ijarets.org

output zero. In order to make a gate reversible additional input and output lines are added so that a one to one mapping exists between the input and output. This prevents the loss of information that is main cause of power dissipation in irreversible circuits. The input that is added to an m x n function to make it reversible is known as constant input (CI). All the outputs of a reversible circuit need not be used in the circuit. Those outputs that are not used in the circuit is called as garbage output (GO). The number of garbage output for a particular reversible gate is not fixed. The two main constraints of reversible logic circuit is

в

0

1

0

1

C

0

0

0

1

Α

0

0

1

1

- Fan out not allowed

- Feedbacks or loops not allowed.

| Fig.1.Truth table of conventional AND gate Fig.1 shows the truth table of conventional AND gate.In       |

|----------------------------------------------------------------------------------------------------------|

| order to make this gate as reversible one input and two outputs are to be added so that it becomes a 3x3 |

| reversible gate. The main criteria while designing a reversible logic circuit is the minimization of the |

| above mentioned parameters (CI, GO).                                                                     |

#### **3. DESIGN OF PROPOSED QLUT**

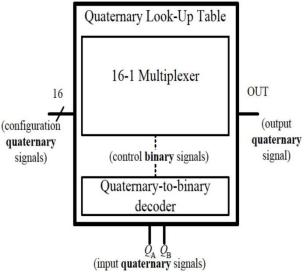

The proposed 2-input and 1-output QLUT is shown in Fig. 2. For this given QLUT complexity, 16 quaternary configuration inputs are necessary, one for each feasible aggregate of the two quaternary inputs. The configuration word defines the reconfigurable quaternary function. In practice, the input signals are used to select which one of the configuration inputs is attached to the output. The principle concept of the paper proposed is to reduce the interconnection present in the existing circuit. The combinatorial block logic capabilities will assist in understanding the function and switch operation inside the circuit proposed. The subsequent table.2 gives the better readability of the signal fetching and switches operations. The proposed QLUT consists of two main blocks: a 16-1 multiplexer using an array of switches, that establishes a low-resistance path between one configuration input and the output according to the input values; and a quaternary-to-binary decoder, including of a 2-bit analog-to-digital (ADC) frontend followed by combinational logic used to generate the control signals feeding the multiplexer.

I. REVERSIBLE ALU DESIGN

# **3.1 PROPOSED DESIGN**

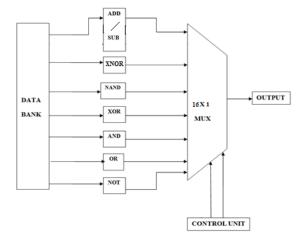

The Fig.5 shows the basic design of an ALU. For implementing a reversible ALU each of these basic components is implemented using reversible logic.

The various sub modules in the design are adder/Subtractor, multiplier and a logical unit. All the operations are performed simultaneously. On the basis of control signal, the required result is provided at the output.

### **3.2 16 BIT ADDER/SUBTRACTOR DESIGN**

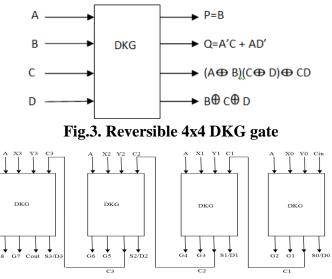

The binary full adder/Subtractor handles each input along with a carry in /borrow in that is generated as carry out/borrow out from the addition of previous lower order bits. If two n bit binary numbers are to be added or subtracted then n binary full adder/Subtractor should be cascaded. A parallel adder/Subtractor is the interconnection of a number of full adder/Subtractor and applying the inputs simultaneously. In this paper a 4 bit parallel adder/Subtractor circuit is designed using a 4x4 reversible DKG gate. Fig.6 shows the reversible DKG gate. This gate can acts as an adder or Subtractor depending on its control input "A". when "A" is zero the gate behaves as a full adder and when "A" is one the gate behaves as a Subtractor. The block diagram of a four bit reversible adder/Subtractor using DKG gate is shown in Fig.7.

Fig.4. Reversible 4bit adder/Subtractor

For implementing a 4bit reversible adder/Subtractor, 4 DKG gates are required. Hence the total gate count for a 4bit adder/Subtractor is 4 and that for a 16 bit adder/Subtractor is 16. Here the carry in (Cin) is propagated from one gate to another gate. The module is designed using VHDL, simulated in modelsim and synthesized using xilinx12.2.

# 3.3 16 BIT LOGICAL UNIT

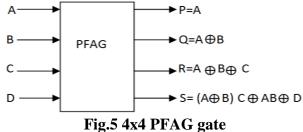

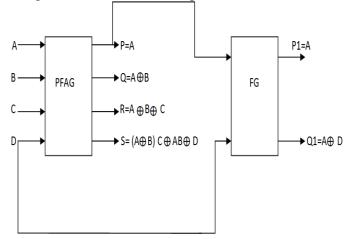

In this paper the logical block is designed using PFAG and Feynman gate. For designing a 1bit logical unit one PFAG and one Feynman gate is required. The truth table of PFAG is shown in Fig.12.

In this design the inputs C and D is taken as the select lines or control lines. When CD=00 the PFAG block acts as an AND gate and the output of the AND operation between A and B is obtained at S. When CD=01 the NAND operation between A and B is performed and the output is obtained at S. When CD=10 the OR operation between A and B is performed and obtained at S. The XNOR operation between A and B is obtained at R.

| Α | В | C | D | Р | Q | R | S |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

|   |   |   |   |   |   |   |   |

Table.1. Truth table of PFAG

When CD=11 the NOT operation of A is carried out and obtained at P1. The XOR operation of A and B is obtained at Q irrespective of the value of C and D. The block diagram of PFAG gate is shown in Fig.11. The design of 1bit logical unit is shown in Fig.12.

Fig.6. Design of one bit logical unit

The above design requires a total of 32 reversible gates (16 PFAG + 16 FG) for implementing a 16bit reversible logical unit that can perform AND ,OR, NOT, XOR, NAND and NOR.

### **4. SIMULATION RESULTS**

All the blocks are modelled using VHDL. The functional verification of the codes is analysed using modelsim 6.5 and synthesised using Xilinx ISE 12.2.

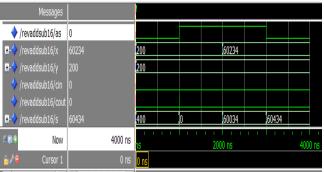

**4.1 16 Bit Reversible Adder/Subtractor**Fig.13 shows the output of 16 bit reversible adder/Subtractor. The inputs to this module are the 16bit data "A", "B" and a control signal "A/S". When the control input is "0", the addition operation is performed and when the control input is "1" subtraction operation in carried out "Cin" indicates the carry in, Cout indicates the carry out or borrow out obtained from the circuit.

Fig.7. Reversible 16bit adder/Subtractor

# **4.2 16 BIT REVERSIBLE LOGICAL UNIT**

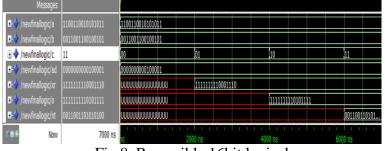

Fig.14 shows the output of reversible 16 bit logical unit.

Fig.8. Reversible 16bit logical

Here A and B indicates the 16bit data. C is a two bit input data that acts as the control signal. Depending on this value the required output results are obtained. AD denotes the AND output, XR denotes the XOR operation, O denotes the OR output and NT denotes the NOT operation.

### **5. SYNTHESIS REPORTS**

The delay and power analysis reports of the various sub modules are also carried out. The power analysis reports are carried out using Synopsys design compiler. The comparison of reversible and conventional sub modules in terms of power and delay is evaluated.

### **5.1 REVERSIBLE ADDER/ SUBTRACTOR**

### **5.1.1 DELAY ANALYSIS**

Table 2 shows the delay analysis of reversible and conventional 4bit adder and Subtractor. It can be deciphered from the figure that reversible adder and Subtractor shows 14% reduction in delay in comparison with conventional adder and Subtractor.

|   | Ripple                                              |       | Reversible | Basic      | Reversible |  |  |

|---|-----------------------------------------------------|-------|------------|------------|------------|--|--|

|   |                                                     | carry | adder      | Subtractor | Subtractor |  |  |

| ĺ | Delay(ns)                                           | 9     | 7.88       | 9.2        | 7.94       |  |  |

|   | Table 2 Delay analysis of this adden and Systemator |       |            |            |            |  |  |

Table 2. Delay analysis of 4bit adder and Subtractor

### **5.1.2 POWER ANALYSIS**

Table 3 shows the power analysis of reversible and conventional adder and Subtractor. Reversible adder and Subtractor shows 25% power reduction in comparison with the conventional adder and Subtractor.

|                                                      | Ripple | Reversible | Basic      | Reversible |  |  |  |

|------------------------------------------------------|--------|------------|------------|------------|--|--|--|

|                                                      | carry  | adder      | Subtractor | Subtractor |  |  |  |

| Power(uW)                                            | 15.26  | 11.39      | 16.57      | 12.35      |  |  |  |

| Table 3. Power analysis of 4bit adder and Subtractor |        |            |            |            |  |  |  |

#### 6. CONCLUSION

The 16 bit reversible ALU is designed by integrating various sub modules that includes adder/Subtractor and logical unit. The logical unit performs AND, OR, NOT, XOR, NAND. The performance evaluation of the various submodules are carried out using synopsys tools and it was found that the circuits designed using reversible logic showed a reduced delay and power. As a future work a reversible divider can also be designed and included into this ALU.

#### REFERENCES

#### JOURNAL PAPER

- 1. Landauer, R., "Irreversibility and heat generation in the computing process", *IBM J. Research and Development*, vol. 5 (3): pp. 183-191, 1961.

- 2. Bennett, C.H., "Logical reversibility of computation", IBM J. Research and Development, vol. 17: pp. 525-532, 1973

- 3. Ravish Aradhya H V, Praveen Kumar B V, Muralidhara K N "Design of Control unit for Low Power ALU Using Reversible Logic" *International Journal of Scientific & Engineering Research Volume 2, Issue 9,* September-2011.

- 4. B. Raghu Kanth1, B. Murali Krishna2, G. Phani Kumar3, J. Poornima4, K. Siva Rama Krishna "A Comparitive Study Of Reversible Logic Gates" *International Journal of VLSI & Signal Processing Applications, Vol.2, Issue 1*, Feb 2012,

#### **CONFERENCE PAPERS**

- 5. HimanshuThapliyal ,NagarajanRanganathan "A New Reversible Design of BCD Adder" *IEEE conference on Design and automation*, 2011 pp.1-4.

- 6. Zhijin Guan, Wenjuan Li, Weiping Ding, Yueqin Hang, LihuiNi"An Arithmetic Logic Unit design based on reversible logic gates "IEEE Pacific Rim Conference on Communications, Computers and Signal Processing (PacRim), 2011.

- 7. Thapliyal H, Srinivas M.B, "Novel Reversible TSG Gate and Its Application for Designing Components of Primitive Reversible/Quantum ALU," *Fifth International Conference on Information, Communications and Signal Processing*, 2006.

- 8. Madhusmita, SisiraKanta, JagannathSatpathy, MerajSaheeL"Design of Arithmetic Circuits Using Reversible Logic Gates and Power Dissipation Calculation" 2010 International Symposium on Electronic System Design, Dec 2010, pp 85-90.

- 9. H.Thapliyal, M.B Srinivas "Novel design and reversible logic synthesis of multiplexer based full adder and multipliers" 48th Midwest Symposium on Circuits and Systems, 2005.